# RISC-V Update

Jonathan Neuschäfer ecc 2017

#### What is RISC-V?

- New general purpose instruction set

- Open standard, no fees

- Lots of interest from the industry

- Hobbyist implementations possible

## Software Status

| binutils/GCC | upstream                     |

|--------------|------------------------------|

| Linux kernel | soon to be upstream          |

| glibc/musl   | waiting for Linux            |

| FreeBSD      | upstream                     |

| LLVM         | WIP, partially upstream      |

| coreboot     | upstream, needs some work :) |

#### Virtual Platforms

- Spike

- the golden reference

- currently the main focus of coreboot/RISC-V

- QEMU

- RISCVEMU

- lots of Virtio

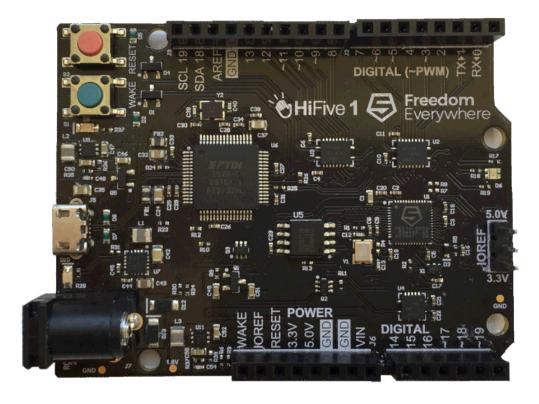

### Hardware: SiFive

- HiFive 1

- microcontroller

- non-trivial clock tree

- U54-MC devboard announced for 2018 Q1

- DDR memory, multicore

- "RISC-V Meets Linux"

### Hardware: lowRISC

## config string → devicetree

```

/dts-v1/;

platform {

/ {

vendor ucb;

compatible = "ucbbar, spike-bare-dev";

arch spike;

memory@80000000 {

device type = "memory";

};

reg = <0 0x80000000 0 0x40000000>;

ram {

};

0

soc {

compatible = "ucbbar, spike-bare-soc", "simple-bus";

addr 0x80000000;

ranges;

size 0x40000000;

clint@2000000 {

};

compatible = "riscv,clint0";

interrupts-extended = <&intc 3 &intc 7>;

};

req = <0 0x2000000 0 0xc0000>;

rtc {

};

addr 0x40000000;

};

cpus {

cpu@0 {

core {

compatible = "riscv";

0 {

riscv, isa = "rv64imafdc";

clock-frequency = <1000000000>;

intc: interrupt-controller {

isa rv64imafdc;

#interrupt-cells = <1>;

timecmp 0x40000008;

interrupt-controller;

compatible = "riscv,cpu-intc";

ipi 0x40002000;

};

};

};

};

```

# Supervisor Binary Interface

```

sbi_putc = -2000

SBI_PUTC = 1

li a0, 'H'

li a0, 'H'

jalr zero, sbi_putc

li a7, SBI_PUTC

ecall

li a0, 'i'

li a0, 'i'

li a7, SBI_PUTC

jalr zero, sbi_putc

ecall

```

#### Future Work

- COLLECT\_TIMESTAMPS

- other architectures have it, and it's a cool feature

- RISC-V Physical Memory Protection

- prevent supervisor from overwriting our code

- optional resident code and SBI

- Linux (currently) needs it

- but I think Ron is right¹

### That's it!

- Thank you for listening

- Questions?